この記事でわかること

「シーケンス制御とは」の簡単な説明をします。

ハード回路でシーケンス制御を実現するために有接点リレー(機械式リレー)方式と無接点リレー方式(ロジックIC)が有ります。このシーケンス回路の基本となる論理演算回路について説明をします。

論理演算回路(NAND、NOR、NOT(INV))とLatch(ラッチ)の回路について、機械式リレーとロジックICで比較、真理値表で動作を説明。差異を説明します。

機械式リレーのラッチについては、動作を図で説明します。

本回路は、【シーケンス制御をハード回路で実現】シリーズの論理演算回路編として、投稿しました。

本シリーズは、他に

・ラッチ回路シミュレーション編

・回路例 編

が有ります。

TINA-TI回路シミュレーション方法については、ここを参照。

シーケンス制御とは

予め定められた順序または、手続きに従って制御の各段階を逐次進めていく制御です。

日本工業規格(JIS)の旧規格 C0401 に定義されています。

シーケンス制御は、全自動洗濯機・エアコンといった私達の身の周りにある家庭用電気器具をはじめ、信号機・自動販売機・工場の産業ロボットや自動化設備・ビルのエレベーターや自動ドア・発電所や変電所に至るまで、さまざまな装置や設備に使われています。単なるスタート/ストップに限る単純なものから複雑な信号処理を必要とする大規模なものまで存在しており、あらゆる分野で活用され、自動化・省力化に大きく貢献しています。

シーケンス制御を実現する具体的方式

- 有接点リレー方式 (ハード回路)

リレーシーケンス(Relay Sequence)とも呼ばれ、電磁リレーをスイッチとして利用し制御する方式です。表現方法としてシーケンス図が用いられます。負荷容量が大きいことや電気的ノイズに安定なことなどから、電動機の制御に応用される。昭和30年代から昭和50年代までは、リレー回路によって構成されたシーケンス制御回路が普通でした。利用実績があります。 - 無接点リレー方式(ハード回路)

ロジックシーケンスと呼ばれ、トランジスタやICなどの半導体を用いた論理素子をスイッチとして利用して制御する方式である。表現方法として論理回路図が用いられる。物理的動作がないため有接点に比べて動作が速く機械寿命が長い。一度作成した回路は容易に変更出来ません。 - PLC方式(プログラマブルロジックコントローラ) (ハード回路+ソフト)

これはパソコンや専用の入力機器を利用して、制御内容をあらかじめプログラムによって表現し、これを逐次実行することによりシーケンス制御を行う装置です。制御内容の複雑化や高度化の要請が高まり、現在では最も多く用いられている。 - マイコン方式(ハード回路+ソフト)

既存のマイコンとソフト開発ツール(ソフト言語は、C言語等)を利用して、制御内容を予めプログラムによって表現し、これを逐次実行することによりシーケンス制御を行う装置です。

一般的に拡販装置に専用に製作され、小型化、減価に寄与します。

「シーケンス制御」『フリー百科事典 ウィキペディア日本語版』。2023年12月27日 (水) 03:29より、引用しました。

”マイコン方式”については、新たに追記しました。

本記事は、シーケンス制御をハード回路で構成する基本の論理演算回路(ラッチ回路を含む)

- 有接点リレー方式(機械式リレー)

- 無接点リレー方式(CMOS(Complementary Metal-Oxide-Semiconductor)ロジックIC)

について比較、差異について説明します。

機械式リレーとロジックICの論理演算回路比較

機械式リレーは、

リレースイッチを開/閉して、論理演算回路を構成します。

CMOSロジックICは、

P型・N型のMOSFETの回路構成でON(ハイ出力)/OFF(ロー出力)して、論理演算回路を構成します。

機械式リレーとロジックICの論理演算回路の比較回路を下記に示します。

論理演算回路で使われている、記号と注意点について

機械式リレーの信号・電源

- input:H=VDD2レベル、L=GND2レベル

- output:H=VDD1レベル、L=GND1レベル

- VDD1:例 DC120W出力に対応 接点(各機械式リレーの仕様によります。)

- VDD2:例 DC3V~100V入力 コイル(各機械式リレーの仕様によります。)

- GND1:VDD1のグランド(0V)

- GND2:VDD2のグランド

GND1とGND2は、別又は、共通グランドどちらでも問題ありません。

機械式リレーの抵抗Rの値について

( 抵抗R << outputに接続する負荷抵抗 )の関係に有ること。

かつ、抵抗Rは、定格電力値以下であること。

かつ、(VDD/R< 接点定格電流)の関係に有ること。

ロジックICの信号・電源

- input:H=VDD1レベル、L=GND1レベル

- output:H=VDD1レベル、L=GND1レベル

- VDD1:DC3.3V/DC5V 入出力値

- GND1:0V

下のセル図は、VDD1とGND1は、省略しています。

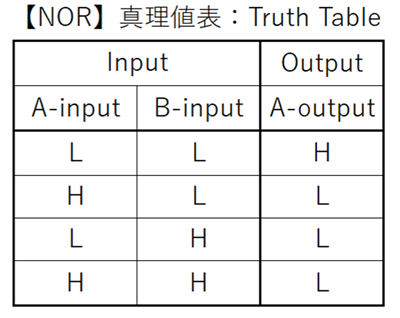

真理値表の値

- H:VDD1レベル

Input:機械式リレー:例 DC3V~100V、ロジックIC:DC3.3V/DC5V

Output:機械式リレー:例 DC120W以下、ロジックIC:DC3.3V/DC5V

機械式リレーについては、各機械式リレーの仕様によります。 - L:GND1レベル(0V)

注意:

- 保護回路については、各部品メーカーの推薦、周辺回路等の影響を考慮により付加有無を判断します。今回、保護回路は割愛いたします。

- TTL(transistor-transistor logic)ロジックICでも、同じ論理演算回路の構成が出来ますが、今回は割愛します。

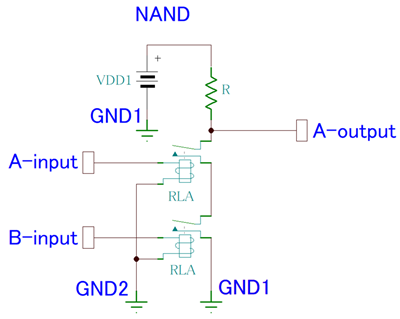

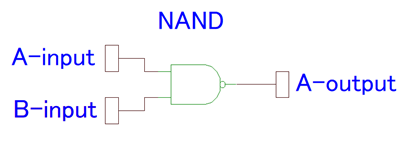

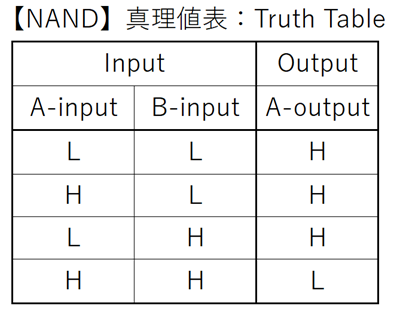

論理演算回路:NAND

NAND:機械式リレー

RLA:A接点リレー

NAND:ロジックIC

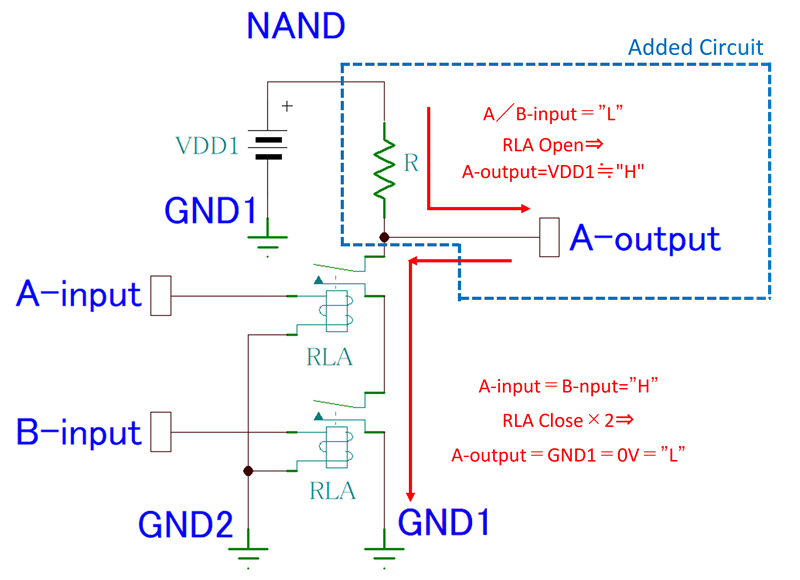

機械式リレーとロジックICの論理演算回路比較の際の追加説明

ロジックICと比較するため、下記回路部を(Added Circuit部(水色の破線))追加しています。

本追加回路により、A-output出力レベル ”H”/”L”を実現しています。

A-input又は、B-inputが”L”、両方”L”レベルの時、機械式リレーRLAのA接点開、A-output=VDD1≒”H”レベルとなります。

この時、A-outputに接続負荷抵抗 >> Rの条件とすること。

A-inputとB-inputが、両方”H”レベルの時、2つの機械式リレーRLAのA接点閉、A-output=GND1=0V=”L”レベルとなります。

以上より、ロジックICセルと同じレベル(”H”/”L”)を出力することが出来ます。

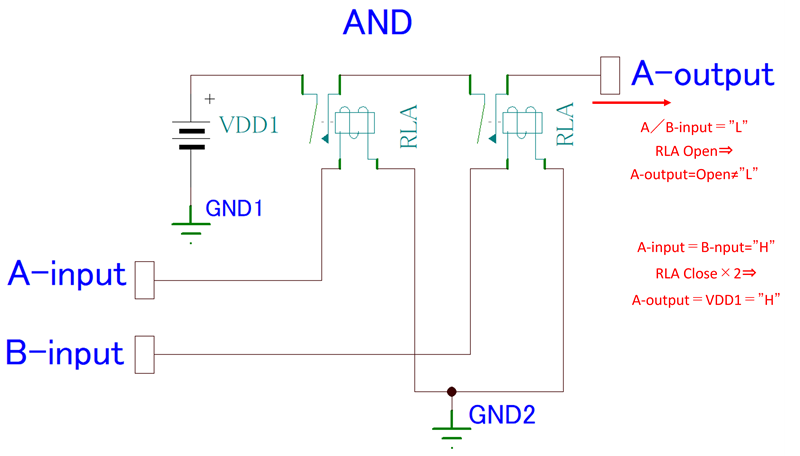

一般的な機械式リレーの論理演算回路(AND回路の場合)

上記、NAND回路の追加回路(Added Circuit部(水色の破線))付けないと、下記 AND回路となります。

A-input又は、B-inputが”L”、両方”L”レベルの時、機械式リレーRLAのA接点開、A-output=Open状態(断線)となります。

A-outputがOpen状態になるので、A-outputに接続する部品は、このOpen状態に対応した処理が必要になる場合が有ります。

A-inputとB-inputが、両方”H”レベルの時、2つの機械式リレーRLAのA接点閉、A-output=VDD1==”H”レベルとなります。

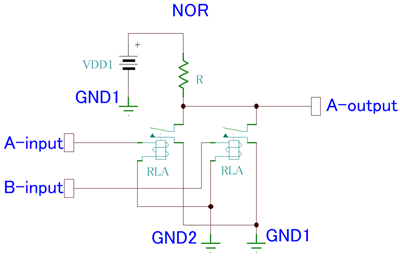

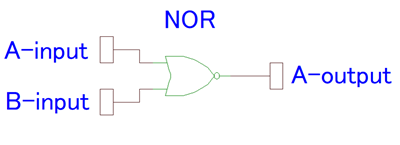

論理演算回路:NOR

NOR:機械式リレー

RLA:A接点リレー

NOR:ロジックIC

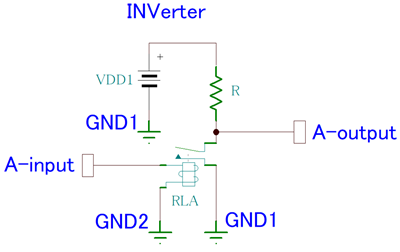

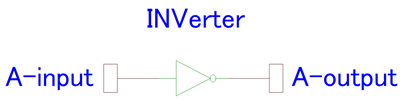

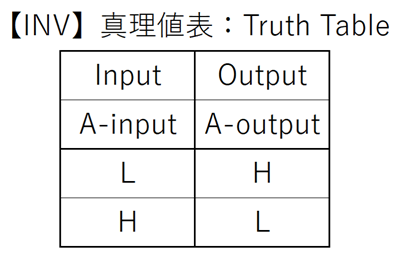

論理演算回路:NOT(INV)

NOT(INV):機械式リレー

RLA:A接点リレー

NOT(INV):ロジックIC

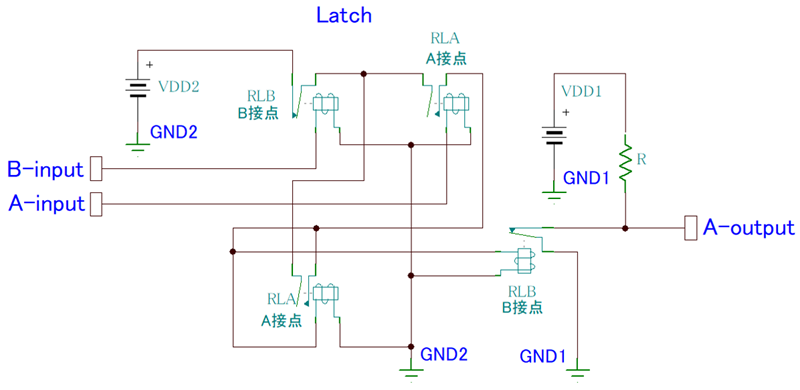

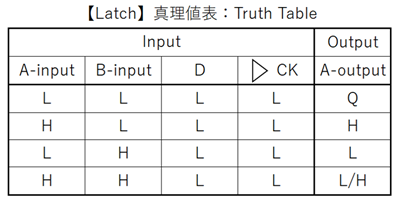

Latch(ラッチ)

SR-Latch:機械式リレー

RLA:A接点リレー

RLB:B接点リレー

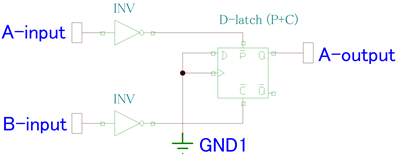

D-Latch セット・リセット付き:ロジックIC

D:GND1固定

▽ CK:GND1固定

NOR、NANDセルで構成するSR-Latchも有りますが、上記の”D-Latch” が一般的に使用頻度が

高いです。

東芝製 TC74HC74を参照

Q:前値保持

D・C:”L”固定

L/H:

機械式リレーは、”L”出力

ロジックICは、”H”出力

機械式リレーには、

”D”・”CK”入力は有りません。

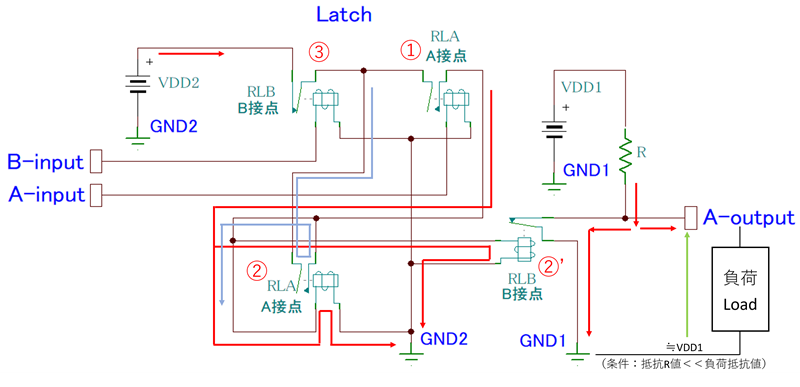

機械式リレー・Latchの動作説明

機械式リレー・Latchの動作を下の図を使い説明します。

初期状態:

A-input=B-input=”L”レベル入力時、A-output=”L”レベル出力

①、②、②’、③リレーのコイル通電無し⇒接点状態変更無し。

②’リレーB接点閉状態となりVDD1の電流は、抵抗Rを通ってGND1側に流れます。A-outputとGND1は同じ電圧レベル”L”(GND1)となります。

セット状態:

A-input=”H”レベル、B-input=”L”レベル入力⇒A-output=”H”レベル出力

A-input=”H”レベル入力①リレーA接点閉状態により、②リレーコイルは通電(VDD2)A接点閉状態となります。ブルー色電流経路により②自体のコイルにも通電します(接点閉状態を保持)、同時に②’リレーコイル通電、B接点開状態となりVDD1の電流は、抵抗Rを通ってA-output側に流れます。

A-outputの出力電圧は、接続されいる負荷側の電圧降下分となります。

抵抗Rの値:

(抵抗R値<<負荷抵抗値)かつ、抵抗R値は定格電力値以下かつ、(VDD/R< 接点定格電流)の条件でRを決めて、出力側:A-output=負荷側の電圧降下分≒VDD1とします。

前の状態保持(A-output=”H”):

A-input=”H→L”レベル、B-input=”L”レベル入力⇒A-output=”H”レベル出力

A-input=”L” レベル入力①リレーA接点開状態となりますが、②リレー自体のA接点閉状態(ブルー色の電流)のままなので②リレーコイルは通電のまま、②’リレーB接点開状態で変わらず、A-output=”H”レベル出力を保持します。

リセット状態:

A-input=”L”、B-input=”H”レベル入力⇒A-output=”L”レベル出力

B-input=”H”③リレーコイルに通電するとB接点開状態となり、②、②’リレーコイルの通電はしないので②A接点開、②’B接点閉状態となり、A-output=”L”レベル出力に変わります。

前の値保持(A-output=”L”):

A-input=”L”、B-input=”H→L”でレベル入力⇒A-output=”L”レベル出力

B-input=”L”レベル入力③リレーB接点閉状態となります。

①、②、②’のコイルは通電しないので①、②A接点開、②’B接点閉状態となりVDD1の電流は、抵抗Rを通ってGND1側に流れます。A-outputとGND1は同じ電圧レベル”L”(GND1)となります。

ラッチ回路のシミュレーションは、ここを参照。

機械式リレーとロジックICの差異ポイント

本記事は、機械式リレーとロジックICセルの論理演算回路を比較した時の気になる差異のポイントを記述しています。

機械式リレー、ロジックICのここの特長は、記述していません。

電圧レベル:

機械式リレー:

コイルの電圧レベル(例 DC3V~100V)

接点の電圧レベル(例 DC120W Max)

各機械式リレーの仕様によります。

出力電圧レベルは、

・接点閉状態⇒電圧レベル出力

・接点開状態出力⇒開放状態(グランド(0V)レベルではありません。)

本記事では、ロジックICセルの出力”L”=グランド(0V)と同じにするため、

出力側の接点開状態⇒”H”出力、接点閉状態⇒”L”出力 になる様に回路を追加しています。

本出力回路は、出力側の接点が開/閉に関係無く(常時)電流が流れる回路となっています。

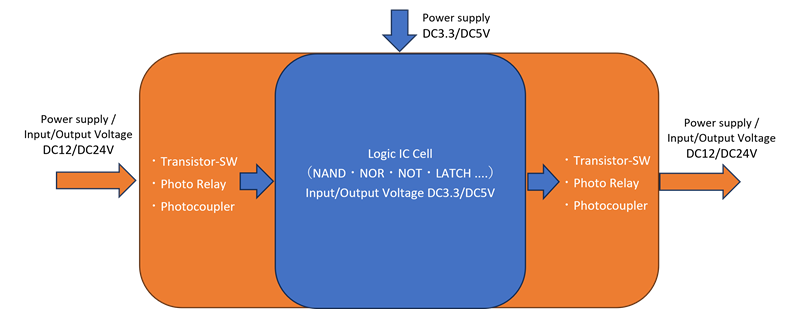

ロジックICの:

電源、信号電圧レベル DC3.3V/DC5V

DC12V/DC24Vのインターフェース電圧の場合は、降圧、昇圧部品(トランジスタ、フォトリレー、フォトカプラ)が必要です。

機械式リレーの電圧(DC12/DC24V)インターフェースに合わせるための概要ブロック図を、下記に示します。

青色:DC3.3/DC5V

橙色:DC12/DC24V

初期設定:

ラッチに初期設定が必要

機械式リレー:

特に無し

ロジックICラッチ系セル:

出力端子Q、/Qには、初期設定が必要です。

動作速度:

機械式リレー:

秒端子

ロジックIC:

ロジックICセルは、ナノ秒単位

降圧、昇圧部品:スイッチトランジスタは、ミリ秒単位

コメント