論理シミュレーション

この記事でわかること

シリアルデータのパリティービット生成回路の論理シミュレーション用回路と出力波形について解説します。

シリアルデータのパリティービット生成回路検証

パリティービット生成回路については、ここを参照。

シミュレーションの回路

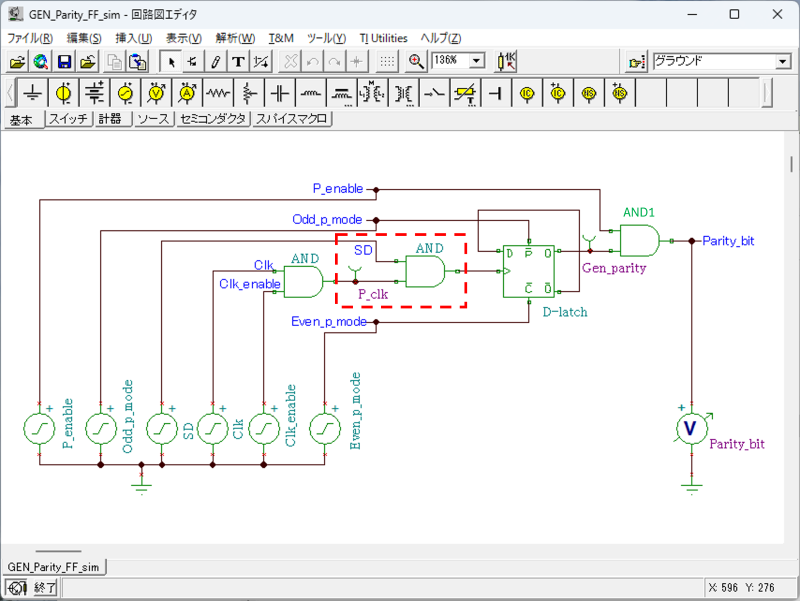

論理シミュレーションを行う回路図を下記に示します。

図-1 偶数パリティービット生成回路 論理シミュレーション

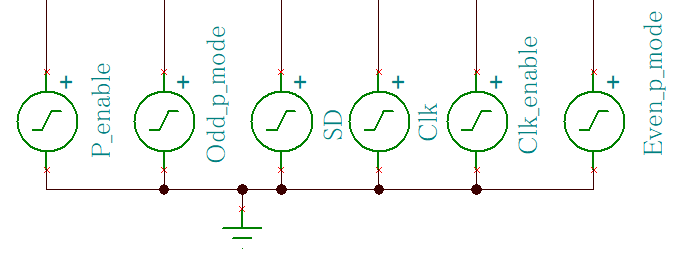

入力には、”電圧ジェネレータ”

出力側には、”電圧計”を追加しています。

シミュレーションの設定

DC電源電圧:5V

入力波形設定:(電圧ジェネレータの設定)

P_enable

電圧ジェネレータ(”シグナル”クリック→”・・・”クリック)→シグナル・エディタの設定

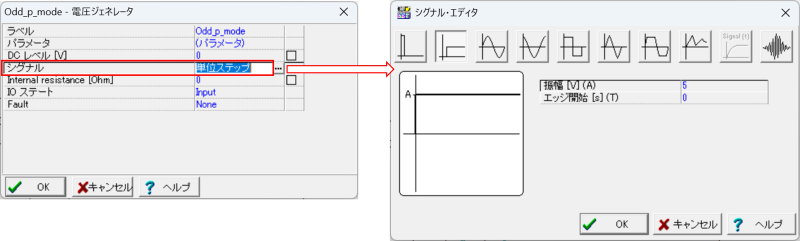

Odd_p_mode

電圧ジェネレータ(”シグナル”クリック→”・・・”クリック)→シグナル・エディタの設定

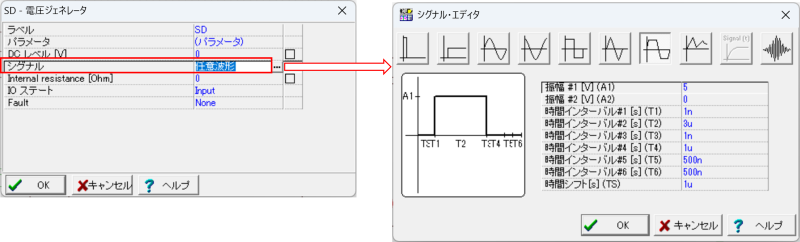

SD

電圧ジェネレータ(”シグナル”クリック→”・・・”クリック)→シグナル・エディタの設定

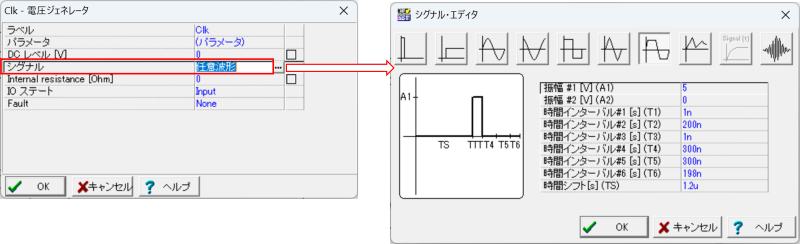

Clk

電圧ジェネレータ(”シグナル”クリック→”・・・”クリック)→シグナル・エディタの設定

Clk_enable

電圧ジェネレータ(”シグナル”クリック→”・・・”クリック)→シグナル・エディタの設定

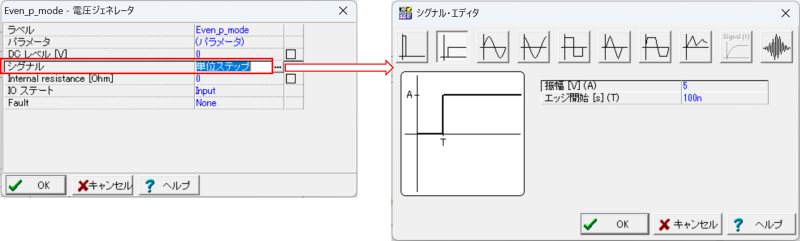

Even_p_mode

電圧ジェネレータ(”シグナル”クリック→”・・・”クリック)→シグナル・エディタの設定

結果検証

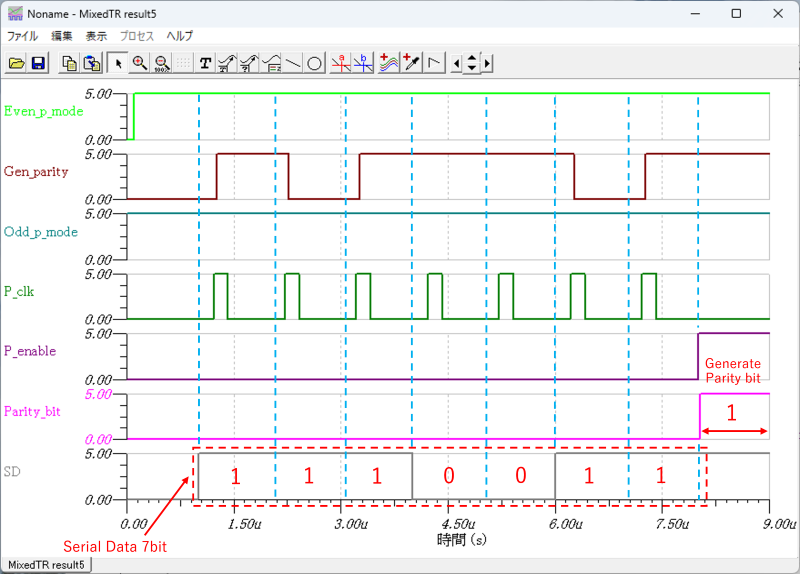

図-1のシミュレーション波形を下記に示します。

図-2:偶数パリティービット生成回路の論理シミュレーション

波形説明:

- Eeven_p_mode:初期値として、”ロー”アクティブにして偶数パリティーモードにします。

(Odd_P_modeは、”ハイ”固定とします。) - SD=”ハイ”毎に、D-latchの”Q”出力を反転させる為、論理積:(SD and P_clk)としてD-latchのクロック端子に入力します。出力信号が、Gen_parityです。

(図-1を参照、赤破線枠のANDセル) - シリアルデータは、SDの図-2の赤破線枠です。”1,1,1,0,0,1,1”。偶数パリティー付加”1”しています。

- 生成した偶数パリティービットは、Parity_bit 信号 “1”と成ります。

(赤字コメント”Generate Parity bit”のタイミングの値”1”です。)

以上より、シリアルデータの偶数パリティービット生成回路の検証が出来ました。

タイミングチャートの詳細は、ここを参照。

コメント