この記事でわかること

受信したパリティービットをチェックする回路の説明と

チェック回路の論理シミュレーションを説明します。

パリティービットチェック回路

値を比較する時は、排他的論理和:EXORセルを使用します。

(パリティービットチェックに限りません。)

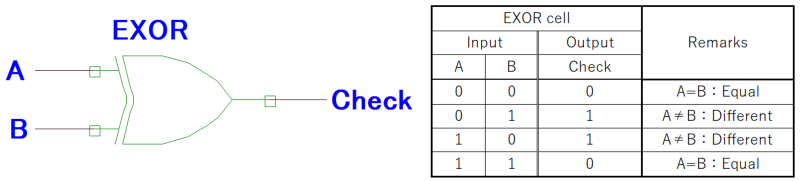

下記に、EXORセルとEXOR真理値表を示します。

図-1:EXORセルとEXORセル真理値表

A=B:正常受信、Check=0

受信したパリティービット”A”と受信したデータから作成したパリティービット”B”の値が同じで有ることをを示します。

A≠B:異常受信、Check=1

受信したパリティービット”A”と受信したデータから作成したパリティービット”B”の値が違う事を示します。

これに、チェックタイミングを考慮した具体的な回路を下記に示します。

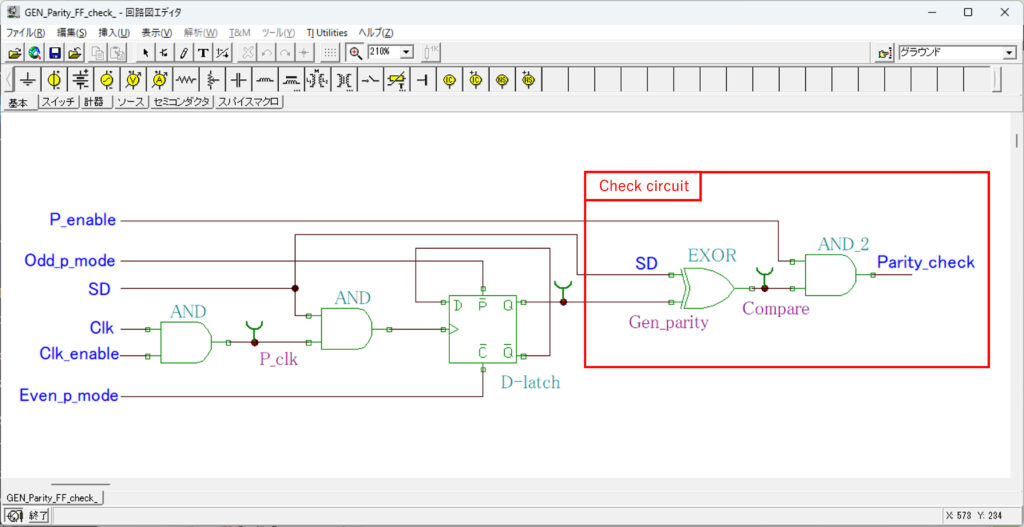

回路

シリアルパリティービット生成回路とパリティーのチェック回路(赤枠)を下記図に示します。

シリアルパリティービット生成回路の詳細はここを参照。

図-2:パリティー生成とパリティーチェック回路

P_enable:Parity enable パリティービットの生成有効タイミング

Odd_p_mode:Odd Parity mode 奇数パリティーモード設定(”ロー”アクティブ)

Even_p_mode:Even Parity mode 偶数パリティーモード設定(”ロー”アクティブ)

SD:Sireal data シリアルデータ

P_clk:Parity clock パリティークロック

Gen_parity:Generate Parity パリティー生成ビット

Compare:Compare SDのパリティーと生成パリティー比較結果

Parity_check:Parity check パリティービットチェック結果

D-latch:エッジ型フリップ・フロップセル

EXOR:排他的論理和セル

AND:論理積セル

Check circuitブロック(赤い枠)

受信したシリアルデータSD(パリティービット)と受信データを元にパリティービット生成Gen_parityをEXORセルで比較します。P_enableは、パリティービットの比較タイミングを決めます。

Parity check 出力信号

0:パリティービット 正常受信

1:パリティービット 異常受信

論理シミュレーション

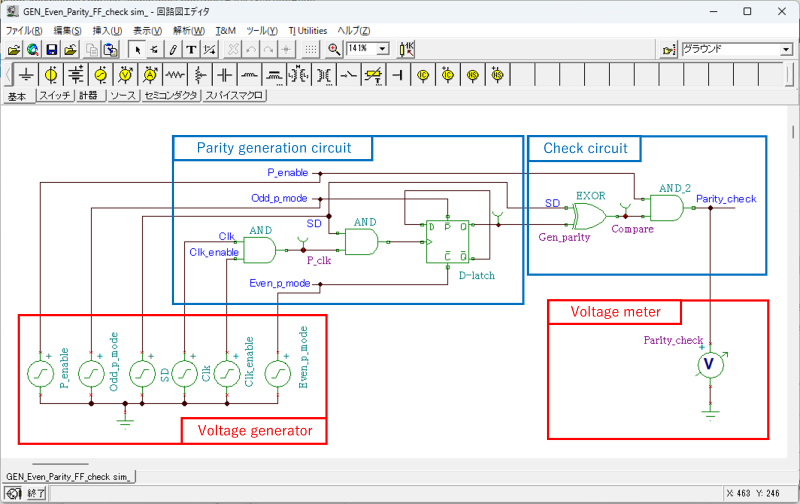

下記、図-3 論理シミュレーション用回路を示します。

偶数パリティービットの生成とチェック回路の論理シミュレーション回路図です。

受信データ(7ビット+偶数パリティービット:1ビット)と生成したパリティービットと比較します。

図-3:論理シミュレーション用回路

Check circuitブロック

受信したシリアルデータSD(パリティービット)と受信データを元にパリティービット生成Gen_parityをEXORセルで比較します。P_enableは、パリティービットの比較タイミングを決めています。

parity generation circuitブロック

SDからパリティービットを生成。

詳細説明は、ここを参照。

Voltage generatorブロック

論理シミュレーション用入力電圧波形。

詳細は、ここを参照。

Voltage meterブロック

電圧計

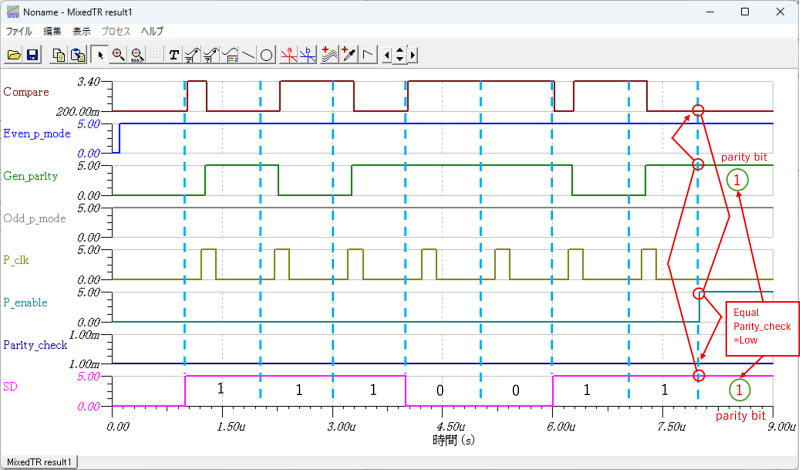

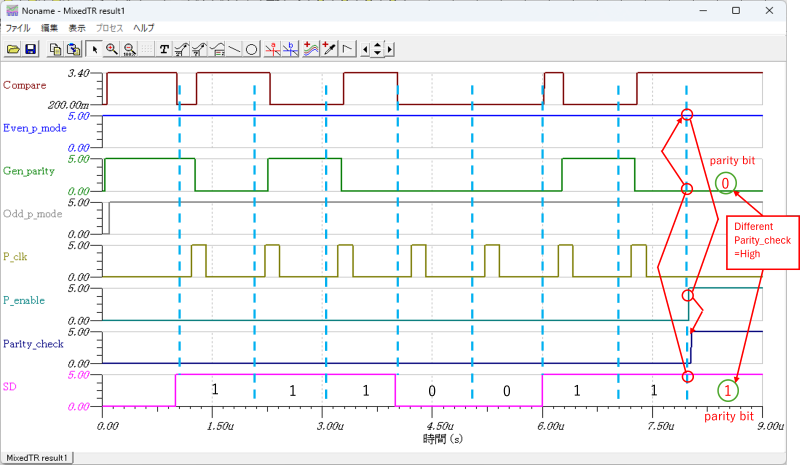

実行結果

下記に、論理シミュレーション結果波形を示します。

正常受信検証版:

注目設定

SD:受信データ+偶数パリティービット

Gen_parity:偶数パリティービットの生成

(初期値:Even_p_mode=0→1、Odd_p_mode=1 固定)

SD(偶数パリティービット)= Gen_parity(偶数パリティービットの生成)→

正常受信、Parity_check=0

図-4:偶数パリティービットのチェック倫理シミュレーション

波形説明:

Gen_parity=1とSDで受信したparity bit=1を比較、同じ値で有ることが確認出来ます。

(丸緑、赤枠部)

上記の値が、同じ事から

parity_check=0となり正常データを受信となります。

異常受信版:

注目設定

SD:受信データ+偶数パリティービット

Gen_parity:奇数パリティービットの生成

(初期値:Odd_p_mode=0→1、Even_p_mode=1 固定)

SDのパリティービットと生成パリティービットを意図的に違う値(異常受信)にして、パリティーエラーを発生させます。

SD(偶数パリティービット)≠ Gen_parity(奇数パリティービットの生成)→

異常受信、Parity_check=1

図-5:奇数パリティービットのチェック論理シミュレーション

波形説明:

Gen_parity=0とSDで受信したparity bit=1を比較、違う値で有ることが確認出来ます。

(丸緑、赤枠部)

上記の値が、違う事から

parity_check=1となり異常データを受信となります。

コメント