この記事でわかること

パリティービットの生成について、簡単な説明します。

具体的な回路作成

・パラレルデータのパリティービット生成回路を説明します。

→基本回路です。(奇数/偶数パリティー2種類有り)

・シリアルデータのパリティービット生成回路を説明します。

→エッジ型フリップ・フロップを利用した回路です。

パリティービットとは

”コンピュータの通信において、与えられた二進数に対し全て全体の偶奇性を保つために与えられる1桁の二進数(つまり0か1)である。パリティービットは最も単純な誤り検出符号ある。”

Wikipediaから引用しました。

データとパリティービットを含だ全体の”1”ビットの偶奇性で、パリティービット値が決まります。

偶数パリティービット付加例:

- 7ビットのデータ:”1110011” →

7ビットデータ+パリティービット(赤数字):”11100111”です。

(8ビット全体で”1”が偶数個(この場合6個)にするため、パリティービット=”1”にします。)

下記に、タイミングチャート図を記述 - 7ビットのデータ:”1100011” →

7ビットデータ+パリティービット(赤数字):”11000110”です。

(8ビット全体で”1”が偶数個(この場合4個)にするため、パリティービット=”0”にします。)

奇数パリティービット付加例:

- 7ビットのデータ:”1110011” →

7ビットデータ+パリティービット(赤数字):”11100110”です。

(8ビット全体で”1”が奇数個(この場合5個)にするため、パリティービット=”0”にします。) - 7ビットのデータ:”1100011” →

7ビットデータ+パリティービット(赤数字):”11000111”です。

(8ビット全体で”1”が奇数個(この場合5個)にするため、パリティービット=”1”にします。)

2種類のパリティービット生成回路

パリティービット生成回路を2つ紹介します。

前提として、

元データ 7ビットから、パリティービット生成する回路作成とします。

パラレルデータのパリティービット生成回路

排他的論理和(EXOR)で実現

排他的論理和(EXOR)とは、

2つの入力のいずれか一方のみが”1”の時、→”1”を出力。

両方”1”又は”0”の時は、→”0”を出力。

上記の論理を利用して、パリティ生成回路を作成します。

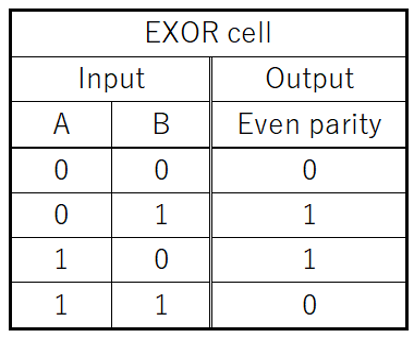

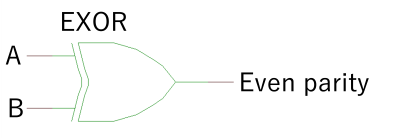

下記に、偶数パリティー真理値表から論理回路に展開します。

偶数パリティー真理値表

EXORセルに展開

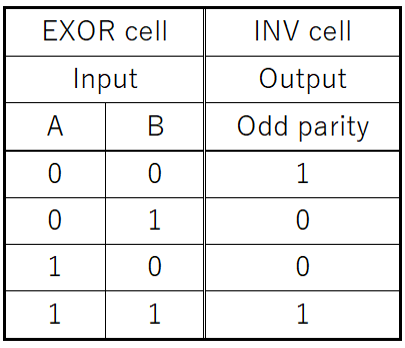

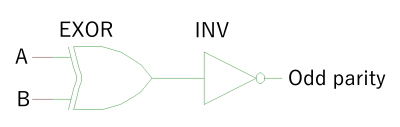

下記に、奇数パリティー真理値表から論理回路に展開します。

奇数パリティー真理値表

EXORとINVセルに展開

元データを7ビットに増やした場合

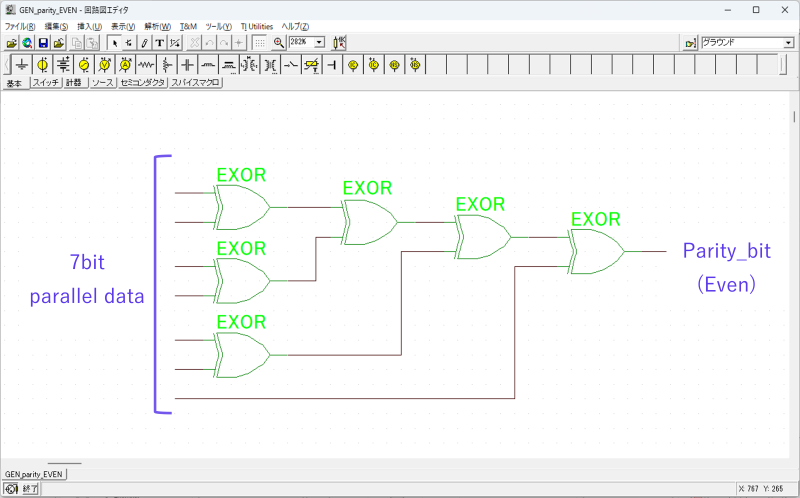

偶数パリティービットの生成回路

7bit data:元データ

Parity_bit:偶数パリティービット

EXOR:排他的論理和セル

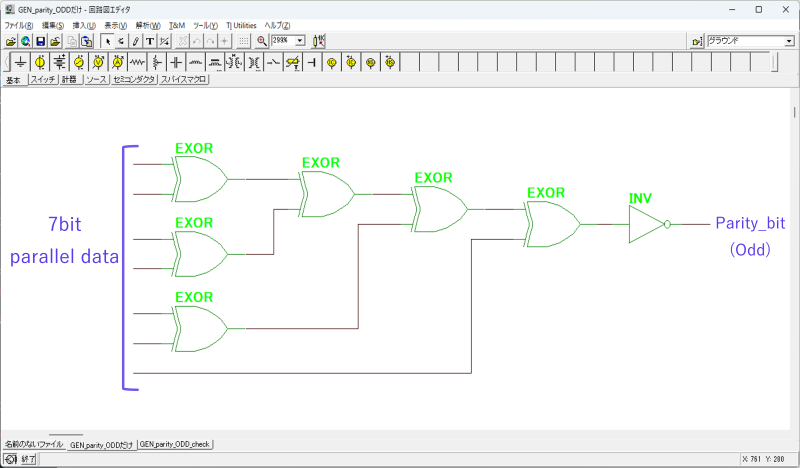

奇数パリティービットの生成回路

7bit data:元データ

Parity_bit:奇数パリティービット

EXOR:排他的論理和セル

INV:インバーター

入力するデータ数(ビット数)に準じて、EXOR(排他的論理和)セル数が増えます。

シリアルデータのパリティービット生成回路

エッジ型フリップ・フロップセルを利用して作成するパリティービットの生成回路です。

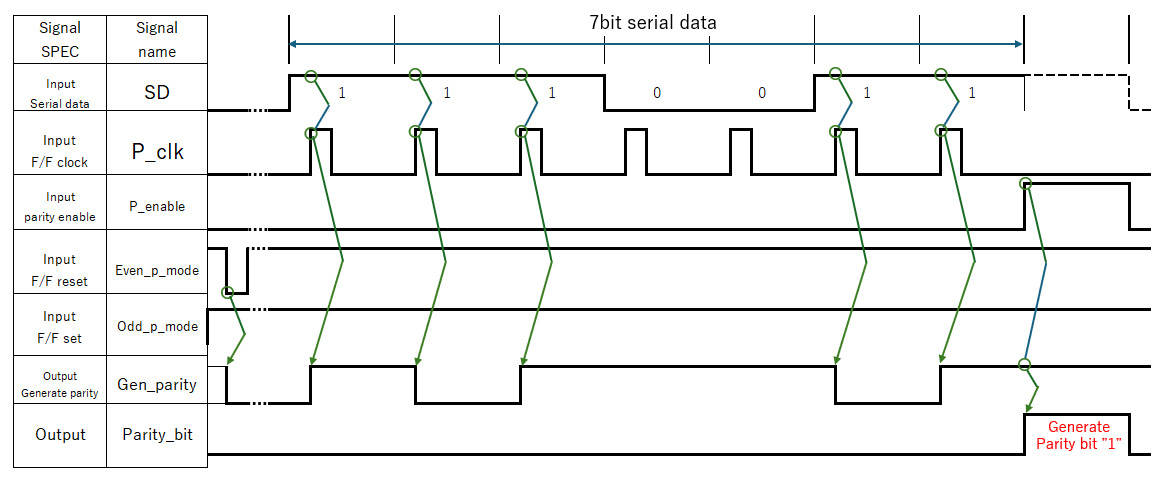

タイミングチャート図

上記の”偶数パリティー例”のパリティービット生成のタイミングチャート図を下記に示します。

Parity_bit波形が、シリアルデータのパリティービット”1”の生成(赤字)です。

各信号については、下記の”生成回路”項で説明します。

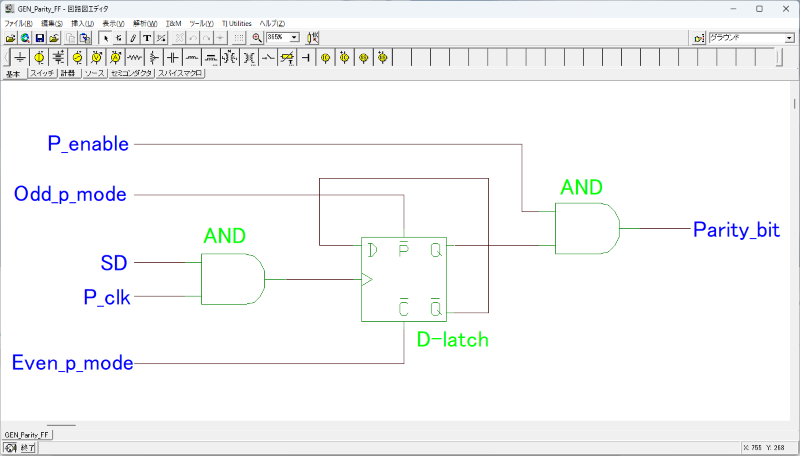

生成回路

エッジ型フリップ・フロップセルを利用した、パリティービットの生成回路を下記に示します。

P_enable:Parity enable パリティービットの生成有効タイミング

Odd_p_mode:Odd Parity mode 奇数パリティーモード設定(”ロー”アクティブ)

Even_p_mode:Even Parity mode 偶数パリティーモード設定(”ロー”アクティブ)

SD:Sireal data シリアルデータ

P_clk:Parity clock パリティークロック

Prity_bit:Parity bit パリティー生成ビット

D-latch:エッジ型フリップ・フロップセル

AND:論理積セル

動作説明:

偶奇性により、D-latchセルの初期値を変えます。

奇数パリティーの場合:

D-latchセルの初期値をQ=”1”出力にします。(Odd_p_mode ”0”入力信号)

偶数パリティーの場合:

D-latchセルの初期値をQ=”0”出力にします。(Even_p_mode ”0”入力信号)

D-latchの/Q端子出力値をD端子入力へ帰還し反転値出力(トグル状態)にします。

この反転回数は、元データの”1”の数により決まります。

P_enable信号は、パリティービットを生成する有効タイミングを決めParity_bit を出力します。

基本回路は固定化され、シリアルビット数(パリティー対象の元データ数)に影響されない回路です。

別記事で、論理シミュレーションを行う予定。

コメント