この記事でわかること

”【状態遷移図(ステートマシン図)から論理回路設計】-1”の続編です。

先編の”状態遷移(ステートマシン)基本論理回路構成図”中の”組合せ論理回路”部を表で解説後、実論理回路図を作成します。

”組合せ論理回路”部を解説

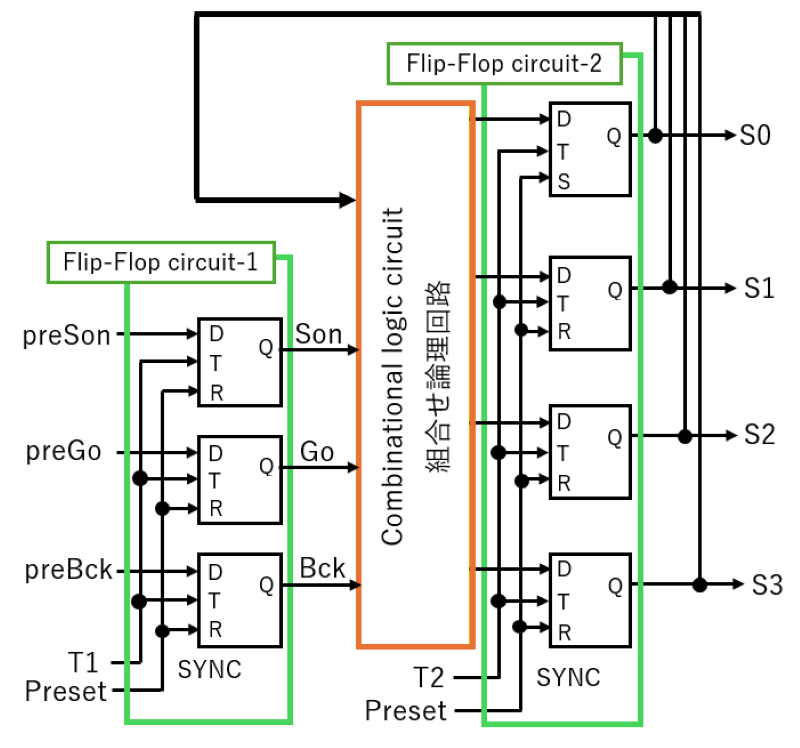

状態遷移(ステートマシン)の”基本論理回路構成図”を下記に示します。

このブロックに”組合せ論理回路”部(橙枠)が有ります。

状態遷移(ステートマシン)基本論理回路構成図

上図、状態遷移(ステートマシン)基本論理回路構成図の説明は、ここを参照。

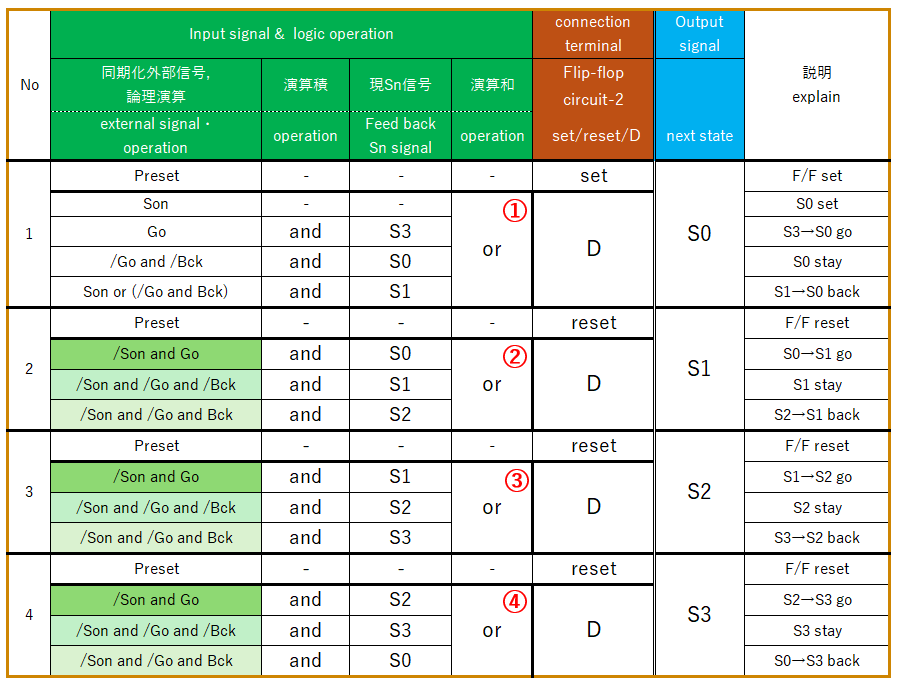

状態遷移図(ステートマシン図)の”組合せ論理回路”部(橙枠)の論理を整理するために、表にしました。

”組合せ論理回路”部演算表

上表の説明:

”No”欄

No1⇒S0(次の状態)を決める演算式です。以下、同様にNo2⇒S1、No3⇒S2、No4⇒S3を決める演算式です。

”Input signal & logic operation”欄(緑部)

Preset入力信号は、S0の”ハイ”レベル出力、S1、S2、S3は、”ロー”レベル出力、

Son、Go、Bck入力信号を各条件により”and”(行ライン)、”and”した演算式をNo毎に”or”します。

(各条件は、”【状態遷移図(ステートマシン図)から論理回路設計】ー 1”の状態遷移図を参照)

”connection terminal”欄(茶部)

Preset入力信号が、接続しる端子を示します。”Flip-flop circuit-2”部のset/reset端子です。

”or”(①、②、③、④)した信号に接続する端子を示します。”D”:”Flip-flop circuit-2”部のD端子です。

”Output signal”欄(青部)

同期化前の状態出力信号(S0、S1、S2、S3)です。

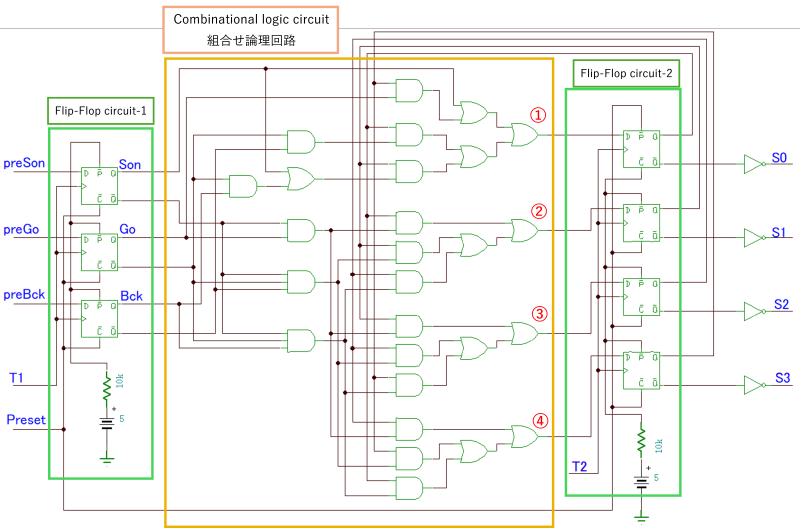

実論理回路

仕様例の状態遷移(ステートマシン)の実論理回路を下記に示します。

実論理回路図

説明:

”Flip-flop-1”部

外部要因の非同期信号preSon、preGo、preBckをT1信号のタイミングに、同期化してSon、Go、Bck信号を生成します。

”組合せ論理回路”部

上表の①、②、③、④は、本ブロック部の①、②、③、④に対応します。

”Flip-flop-2”部

外部・内部要因の条件により生成した各信号(①、②、③、④)をT2信号のタイミングに、同期化して状態信号(S0、S1、S2、S3)を生成します。

注意:

各状態で目的の動作を実行するために、各状態信号(S0、S1、S2、S3)を根幹として使います。

各状態信号(S0、S1、S2、S3)を演算条件に追加して各状態の論理回路設計をします。

”Flip-Flop circuit-1/-2”は、エッジ型フリップ・フロップを採用します。

本フリップ・フロップセルの/P、/C端子は、”L” レベルアクティブのため、Preset信号は”L”レベルアクティブタイミングにします。

ロジックICセルは、上表の演算式と同じにしました。よってゲート数の最小化を意識した論理回路になっていません。

本実論理回路をTINA-TIシステムの論理回路シミュレーションで動作を確認します。

コメント