この記事でわかること

”状態遷移図”(ステートマシン図)から論理回路設計方法について、実践的に例を挙げた記事です。

論理回路を作成する方法として、状態遷移図を利用します。

・簡単な”状態遷移図とは”の説明

・例を使い、状態遷移図と”タイミングチャート”の説明

・この例から”基本論理回路構成”を説明

別記事ですが、本例から”実論理回路”作成、”論理回路シミュレーション”を実行する予定です。

状態遷移図とは(概要)

状態遷移図(ステートマシン図)とは、ある状態(ステート)が、外部又は内部の要因(ここでは、信号)により、移り変わるという事を、図を使い具現化したものです。

装置設計の状態遷移は、装置全ての状態を網羅します。

この全て網羅された状態が設計の根幹となります。全てが網羅されている状態なので設計漏れが有りません。

基本的に各状態内で実行する回路は、別途設計します。

”状態遷移図”と”ステートマシン図”は、同じと考えています。

状態遷移は、ソフトに展開することも出来ますが、本記事では、論理回路設計(ハード)で実現する方法を記事にします。

状態遷移図を作成する時は

状態遷移図を作成する時とは、エレキ設計工程の始めに作成します。設計の始めに作成して全ての状態を網羅することが、大きなポイントだと思います。

(始めの工程で設計漏れをふせぐことが可能なので、設計工程の戻り作業を無くします、又は後戻りを最小限に抑える事を可能にします。設計工程中に、仕様変更が有っても状態遷移図で全状態が網羅してて整理されているので柔軟に対応可能です。)

私の思いですが、プレゼンテーション、デザインレビュー等で状態遷移図がしばしば見られます。状態遷移図を見る方が状態遷移図の書き方・仕様について全て理解している方、またそうで無い方がいます。分かりずらい、紛らわしい場合は、注釈文を追加して誤解を防ぎましょう。

状態遷移図から論理回路設計

状態遷移図(ステートマシン図)から論理回路設計します。

仕様例を決めて、状態遷移図作成→タイミングチャート作成→論理回路構成図を説明をします。

別投稿ですが、”論理回路構成図”から実論理回路をTINA-TIシステムで作成します。

そして、同システムで論理回路シミュレーションを実行します。

基本仕様例

基本仕様:

- 電源立ち上げ時、”S0”状態

- ”状態”は、4個有り

- ”状態”を進む、戻り遷移の制御有り

(進む遷移は、S0→S1→S2→S3→S0・・) - どの”状態”で有っても”S0″状態に遷移制御有り

- 遷移移動の優先順位 S0遷移>遷移進む>遷移戻り>遷移無し(”状態”変化無し)

状態遷移に使う信号の整理

上記、仕様例から回路の主な信号(赤字)を決めます。

外部要因

Preset:初期の起動信号

Son:状態”S0″遷移信号

Go:状態進む遷移制御信号(例:S0→S1→S2→S3→S0)

Bck:状態戻り遷移制御信号(例:S0→S3→S2→S1→S0)

各パルスの有効幅は、同期化信号の周期(T1)より大きいとします。

内部要因

同期信号T1,T2入力信号

(同期化信号については、状態遷移図では表現されていません。タイミングチャート図で記述します。)

”現状態”出力信号S0~S3を帰還した入力信号

各”状態”active(=1)

S0:S0状態出力信号

S1:S1状態出力信号

S2:S2状態出力信号

S3:S3状態出力信号

全体を、同期式で制御します。

状態遷移

上記の基本仕様と外部・内部要因を考慮して、状態遷移図(ステートマシン図)を作成します。

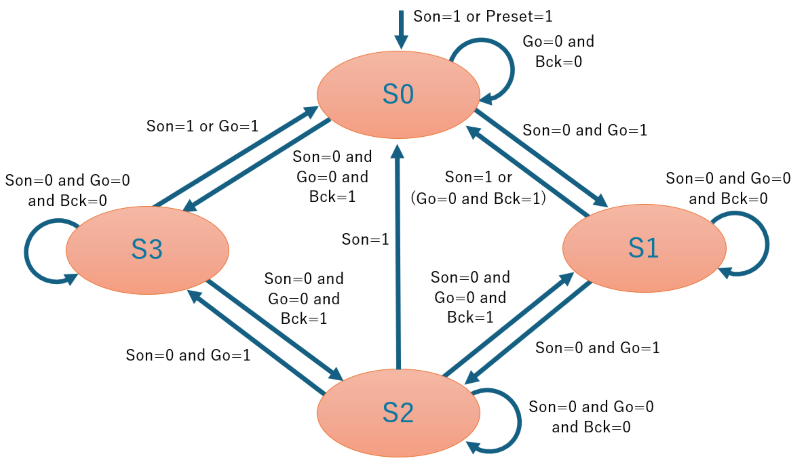

状態遷移図(ステートマシン図)

状態遷移図の説明:

状態(Sn)が、外部の4個入力信号(Preset、Son、Go、Bck)と内部の4個の内部信号(S0、S1、S2、S3)の演算(and、or)で4個の状態が遷移する事を示します。

矢印は、外部・内部要因により遷移する方向を示します。

優先順位は、論理演算and条件をつかいます。

基本仕様から、”S0遷移>遷移進む>遷移戻り>遷移無し(”状態”変化無し)”を論理演算表で下記に示します。

状態の優先度と論理演算表

| 優先度 | 状態遷移 Snは、現在の状態 | 信号と論理演算 |

| 1 | S0 | Preset=1 or Son=1 Sn,Go,Bck信号無視 |

| 2 | Sn→Sn+1 | (Son=0 and Go=1)and Sn Bck信号無視 |

| 3 | Sn→Sn-1 | (Son=0 and Go=0 and Bck=1)and Sn |

| 4 | Sn | (Son=0 and Go=0 and Bck=0)and |

上記表の説明

優先順位1:S0遷移

Son入力信号又は、Preset入力信号が”1”になれば、必ずS0出力信号が”1”になります。

Go、Bck入力信号が”1”になっても、上記状態を優先します。

優先順位2:次のSn+1へ進む遷移(Son=Preset=”0”であること)

SonとPreset入力信号の次に優先度が高いGo入力信号です。Go=”1”の時、現状態SnからSn+1に遷移、Sn+1出力信号”1”となります。Go入力信号が”1”固定の場合は、遷移はS0→S1→S2→S3→S0→と回ります。

優先順位3:前のSn-1に戻る遷移(Son=Preset=Go=”0”であること)

Bck入力信号が”1”の時、現状態SnからSn-1に遷移、Sn-1入力信号”1”となります。Bck入力信号が”1”固定の場合は、遷移はS0→S3→S2→S1→S0と回ります。

優先順位4:Snのまま(変化無し)

4本の外部入力信号が全て”0”の時、現状態Snのまま遷移しません。

”1”=”ハイ”(3.3V/5V)レベル

”0”=”ロー”(0V)レベル

タイミングチャート

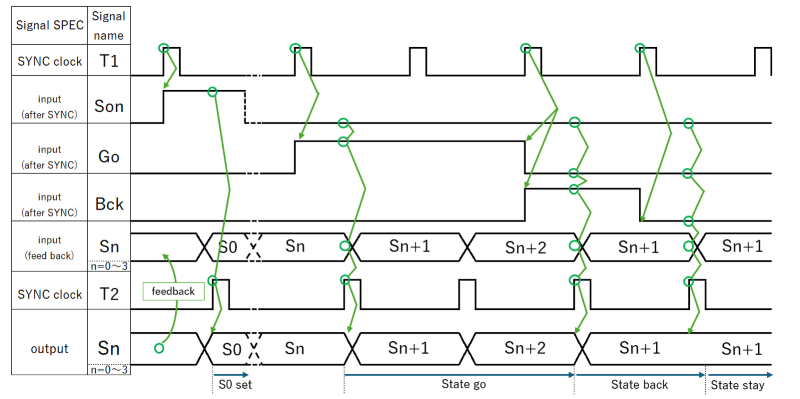

状態遷移図は、時間関係が明確でないのでタイミングチャートを作成して各信号の時間・タイミングを明確にします。

状態遷移図のタイミングチャート図を下記に示します。

各入力信号の優先度も考慮したタイミングチャート図です。

状態遷移のタイミングチャート図

T1信号のタイミングで同期化した、Son、Go、Bck入力信号です。

T2信号のタイミングで同期化した、S0、S1、S2、S3出力信号です。

S0~S3出力信号は、現状状態を論理演算条件とするため信号を帰還します。

緑丸は、論理演算を示します。矢印は論理演算によって得られる信号を示します。

So set:Son”ハイ”レベルで、S0状態

State go:Go”ハイ”レベルで状態が2個遷移

State Bck:Bck”ハイ”レベルで状態が1個戻り

State stay:Son、Go、Bck全て”ロー”レベルのため、状態変化無し

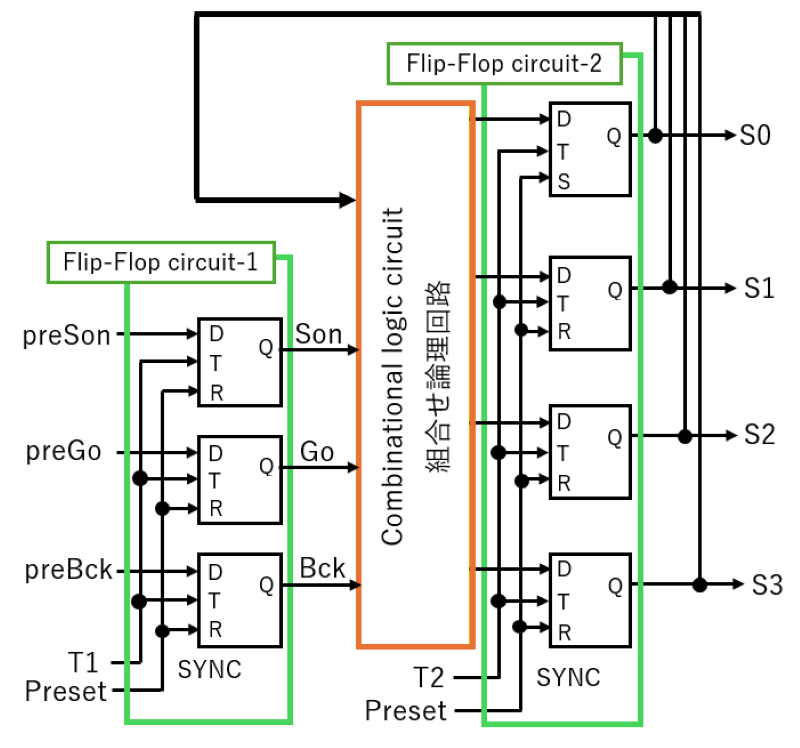

基本論理回路構成図(同期化版)

状態遷移(ステートマシン)を実現するための、基本論理回路構成図を下記にし示します。

状態遷移(ステートマシン)基本論理回路構成図

Preset信号は、同期化せず、”Flip-Flop circuit-1″・”Flip-Flop circuit-2″のセット/リセット端子に接続します。

”Flip-Flop circuit-1″は、T1同期化信号を使い外部信号(preSon、preGo、preBck)を同期化します。

”組合せ論理回路”を次の遷移状態Snを決めます。

”Flip-Flop circuit-2″は、T2同期化信号を使い出力信号(S0、S1、S2、S3)を同期化します。

別投稿ですが、”論理回路構成図”から実論理回路をTINA-TIシステムで作成します。

そして、同システムで論理回路シミュレーションを実行します。

非同期式としては、本ブログの”【シーケンス制御をハード回路で実現】回路 例 編”の”状態遷移図”を参照。

コメント