機械式リレー・ラッチ回路の動作説明は、ここを参照。

機械式リレー、ロジックICの論理演算子セルについては、ここを参照。

TINA-TI回路シミュレーション方法については、ここを参照。

この記事でわかること

ラッチ回路を機械式リレーとロジックICセルで作成、回路シミュレーションを実行します。

回路シミュレーション用回路、環境、結果波形を示します。

機械式リレー、ロジックIC回路 共に、入出力電圧はDC24Vとしました。

セット・リセット ラッチ動作確認をします。

本シミュレーションは、【シーケンス制御をハード回路で実現】シリーズのラッチ回路シミュレーション編として、投稿しました。

本シリーズは、他に

・機械式リレー、ロジックICセル 論理演算回路編

・回路例 編

が有ります。

回路シミュレーションの目的

機械式リレーとロジックICのラッチ動作を回路シミュレーションの結果波形で説明して、セット・リセット ラッチ回路を、機械式リレーとロジックICセルで実現します。

ラッチ・シミュレーション用回路と波形

- 本回路は、ラッチのH/L基本動作が目的のため、抵抗値Rについては検討が必要です。

- 保護回路については、各部品メーカーの推薦、周辺回路等の影響を考慮にして付加有無を判断します。今回、保護回路は割愛いたします。

機械式リレーの回路シミュレーション

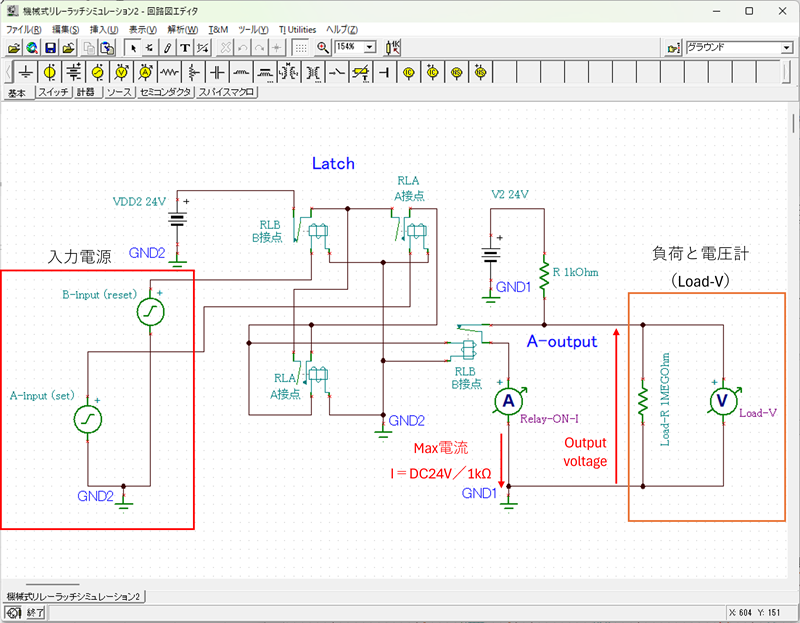

機械式リレー ラッチの回路シミュレーション用回路(Latch)と入力電源、負荷設定を下記に示します。

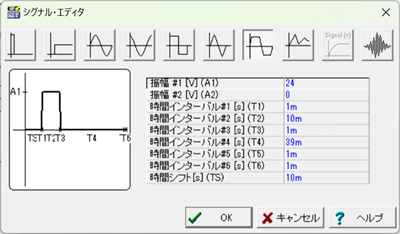

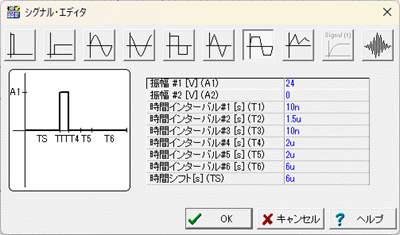

A-inputの”電圧ジェネレータ”の設定

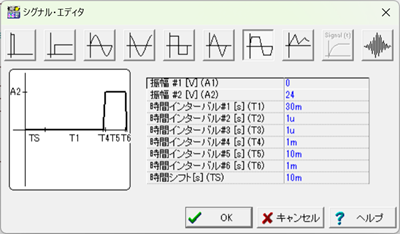

B-inputの”電圧ジェネレータ”の設定

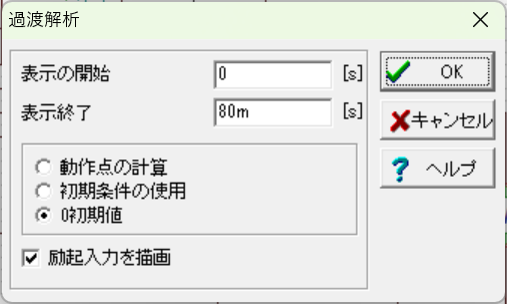

回路シミュレーションの実行:”回路図エディタ”のメニュー⇒”解析(W)”⇒”解析…”を左クリック

上記の設定をして、実行(”OK”左クリック)

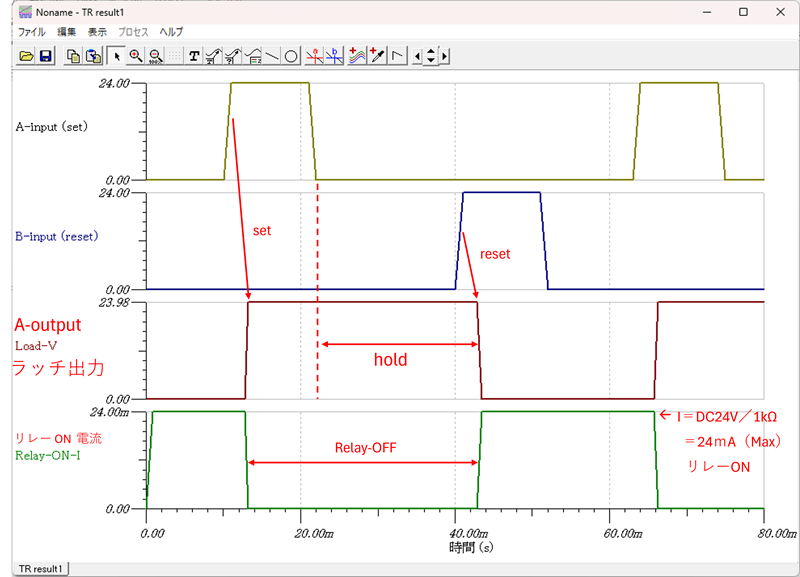

実行結果波形

実行結果波形を下記の示します。

全体は、DC24V電源で動作しています。

シミュレーションの動作速度は、[ミリ秒]単位としました。

(実回路動作では、[秒]単位が良いと思います。)

ラッチの動作内容:

A-input=”H”パルス(セット動作)⇒ A-output=”H”保持。

Bーinput=”H”パルス(リセット動作)⇒ A-output=”L”保持。

セット・リセットラッチ動作を確認出来ました。

ロジックICセルの回路シミュレーション

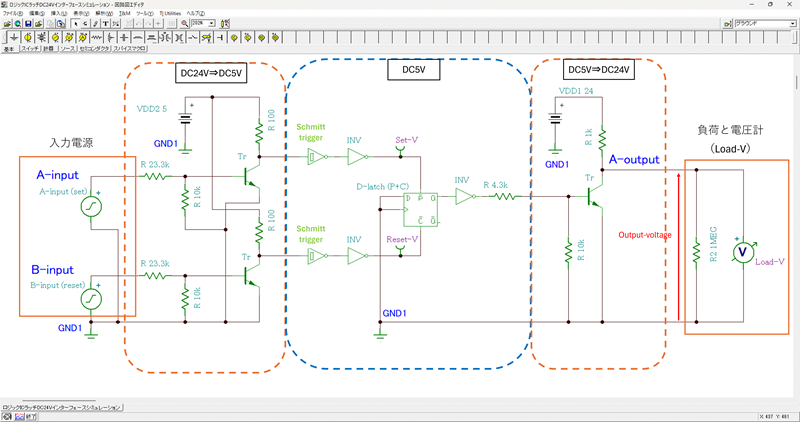

ロジックICセル ラッチの回路シミュレーション用回路(Latch)と入力電源、負荷設定を下記に示します。

ラッチセルは、使用頻度が有る(セット、リセット付きD-latchセル)を採用しました。

例えば、型式:xx74HC74など

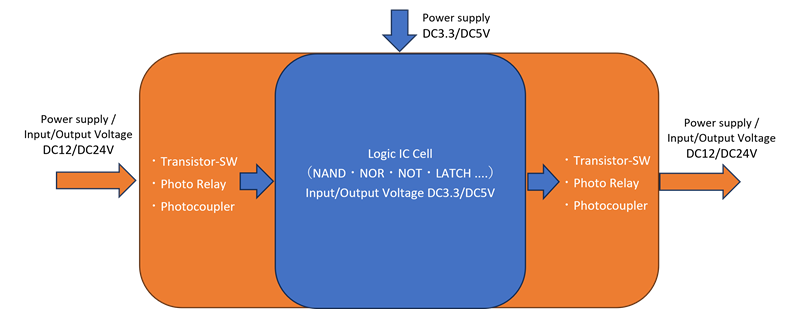

電源、入出力電圧は、DC24V、ロジックセルは電源、信号電圧DC5Vで動作しています。

電源と入出力電圧と部品は、下図の関係です。

橙色:DC24V

青色:DC5/3.3V

インターフェース部品:トランジスタ スイッチ、フォトリレー、フォトカプラを使用

インターフェース部品(トランジスタ スイッチ、フォトリレー、フォトカプラ)の出力信号をシュミットーインバーターセルに接続することを推奨します。

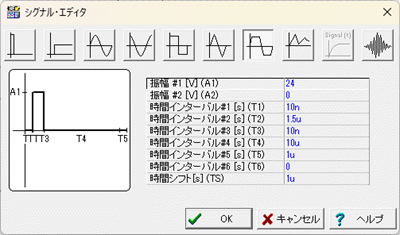

A-inputの”電圧ジェネレータ”の設定

B-inputの”電圧ジェネレータ”の設定

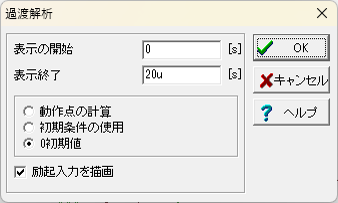

回路シミュレーションの実行:”回路図エディタ”のメニュー⇒”解析(W)”⇒”解析…”を左クリック

上記の設定をして、実行(”OK”左クリック)

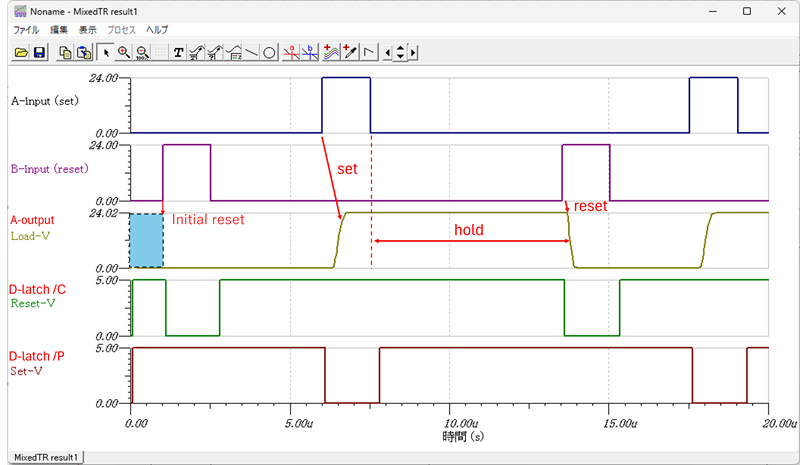

実行結果波形

実行結果波形を下記の示します。

インターフェース部DC24V、ロジック内DC5V電源で動作しています。

インターフェース部品は、トランジスタを使用(デフォルトのSPICEライブラリー使用)

シミュレーションの動作速度は、[マイクロ秒]単位としました。

ラッチの動作内容:

D-latchは、初期設定が必要です。

A-input=”H”パルス(セット)⇒ A-output=”H”保持。

Bーinput=”H”パルス(リセット)⇒ A-output=”L”保持。

セット・リセットラッチ動作を確認出来ました。

まとめ

セット・リセットラッチの動作を、機械式リレーとロジックICセルで実現出来ました。

コメント