この記事わかること

”【状態遷移図(ステートマシン図)から論理回路設計】-2”の続編です。

先編の”仕様例の状態遷移(ステートマシン)の実論理回路”をTINA-TIシステムの論理回路シミュレーションで実行します。入力タイミングは、”【状態遷移図(ステートマシン図)から論理回路設計】-1”

のタイミングチャート図を参考にしました。(一部動作追加)

状態遷移回路の論理回路シミュレーション

シミュレーション設定

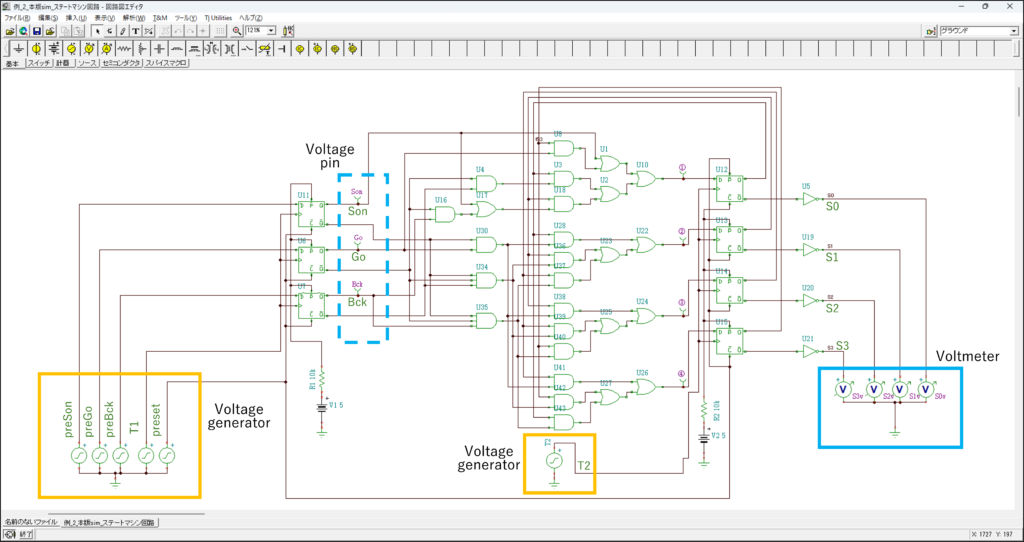

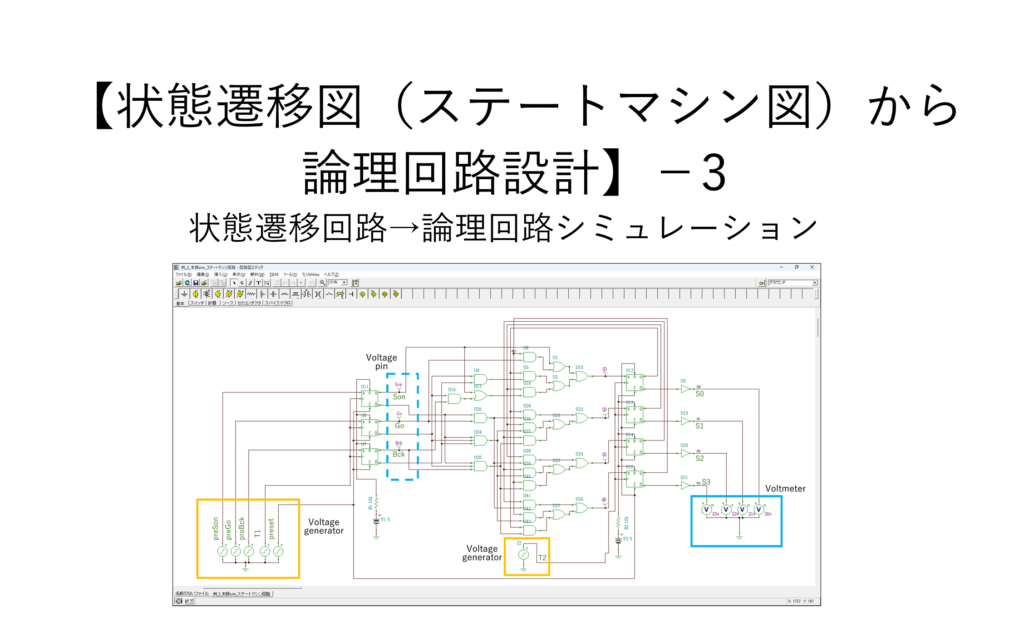

論理回路シミュレーションを行う回路を下記に示します。

TINA-TIシステムのシミュレーション実行方法は、ここを参照。

状態遷移論理回路に、入力信号生成(Voltage generator:橙枠)、波形観測用(Voltage pin:水色破線枠)、出力信号測定(Voltmeter:水色枠)を追加しています。

状態遷移論理回路 論理回路シミュレーション図

入力波形は、”【状態遷移図(ステートマシン図)から論理回路設計】ー 1”のタイミングチャート図を参照しています(一部追加タイミング有り)

DC電源電圧:5V

各入力信号のタイミング設定:(Voltage generator:橙枠)

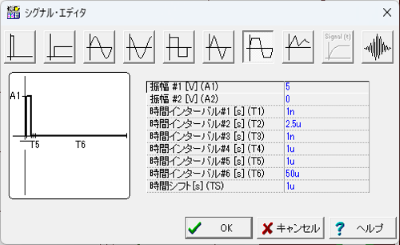

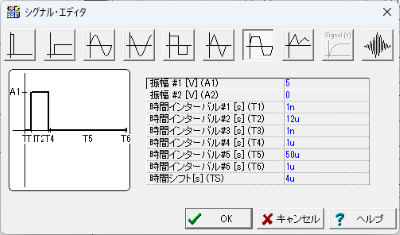

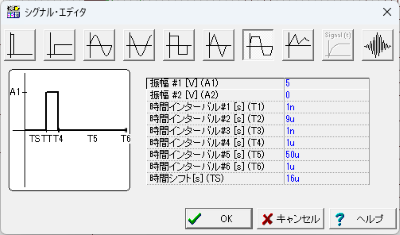

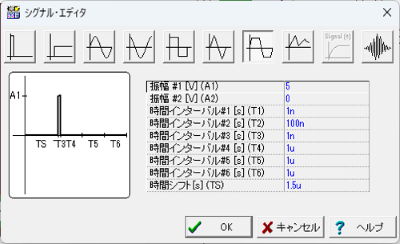

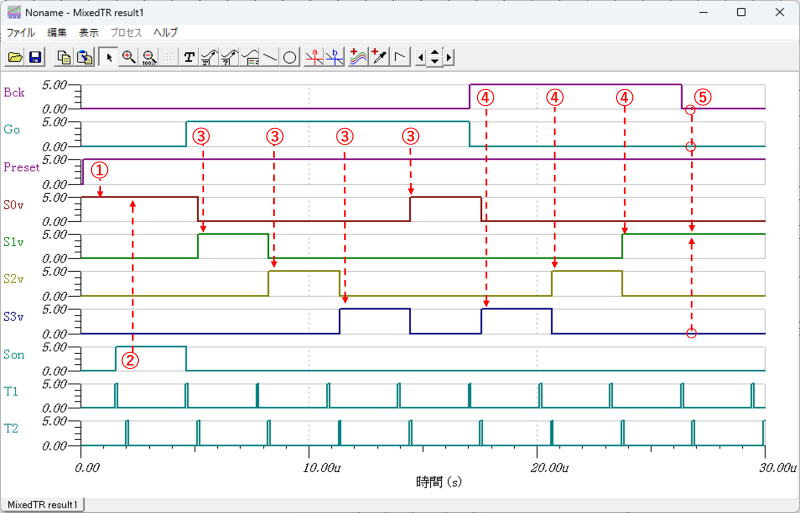

preSon信号の入力タイミング

preGo信号の入力タイミング

preBck信号の入力タイミング

T1信号の入力タイミング

Preset信号の入力タイミング

T2信号の入力タイミング

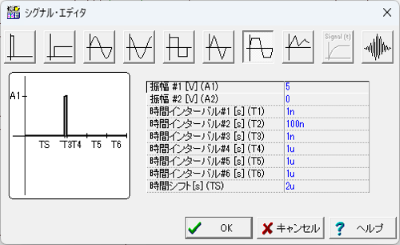

シミュレーション実行波形

論理回路シミュレーションを実行したタイミングチャートを下記に示します。

説明:

- ①:Preset入力信号”ロー”レベルにより、状態:S0v=”ハイ”、S1v=”ロー”、S2v=”ロー”、S3v=”ロー”レベル出力

- ②:Son信号”ハイ”レベルにより、状態:Sov=”ハイ”レベル継続

- ③:Go信号”ハイ”レベルにより、状態:S0v⇒S1v⇒S2v⇒S3v⇒S0v=”ハイ”レベルに

進む遷移 - ④:Bck信号”ハイ”レベルにより、状態:S0v⇒S3v⇒S2v⇒S1v=”ハイ”レベルに戻り遷移

- ⑤:Son=Go=Bck=”ロー”レベル時、状態:S1vのまま

注意:S0v=S0、S1v=S1、S2v=S2、S3v=S3です、

本シミュレーションにより、状態遷移論理回路が、課題である基本仕様に準じた回路で有ることを確認しました。

リンク

コメント